## **Product Description**

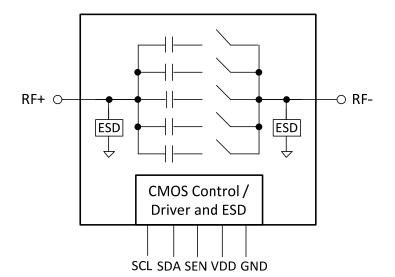

PE621010 is a DuNE™-enhanced Digitally Tunable Capacitor (DTC) based on Peregrine's UltraCMOS® technology. This highly versatile product supports a wide variety of tuning circuit topologies in series or shunt configurations. DTC products provide a monolithically integrated impedance tuning solution for demanding RF applications.

PE621010 offers high RF power handling and ruggedness while meeting challenging harmonic and linearity requirements enabled by Peregrine's HaRP™ technology. The device is controlled through the widely supported 3wire (SPI compatible) 8-bit serial interface. All decoding and biasing is integrated on-chip and no external bypassing or filtering components are required.

DuNE™ devices feature ease of use while delivering superior RF performance in the form of tuning accuracy, monotonicity, tuning ratio, power handling, size, and quality factor. With built-in bias voltage generation and ESD protection, DTC products provide a monolithically integrated tuning solution for demanding RF applications.

Figure 1. Functional Block Diagram

# **Product Specification**

# PE621010

UltraCMOS® Digitally Tunable Capacitor (DTC) Optimized for 2G/3G/4G Impedance Tuning Applications, 100-3000 MHz

#### **Features**

- 5-bit 32-state Digitally Tunable Capacitor

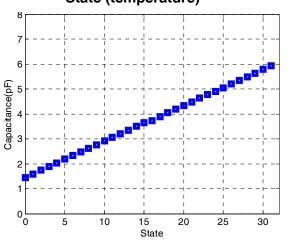

- C = 1.38 5.90 pF (4.3:1 tuning ratio) indiscrete 146 fF steps

- RF power handling (up to +26 dBm, 6 V<sub>PK</sub> RF) and high linearity for diversity applications

- Wide power supply range (2.3 to 3.1V) and low current consumption (typ.  $I_{DD} = 30 \,\mu\text{A} \,@\, 2.8V$ )

- 2 x 2 x 0.55 mm QFN package

- High ESD tolerance of 2kV HBM on all pins

- Applications include:

- Antenna tuning

- Tunable filters

- Impedance matching

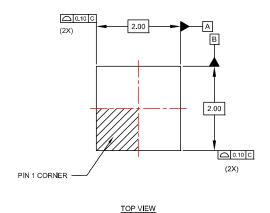

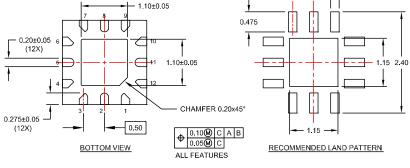

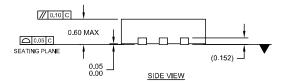

Figure 2. Package Type 12-lead 2 x 2 x 0.55 mm QFN package

# Table 1. Electrical Specifications @ 25 °C, $V_{DD}$ = 2.8V (In shunt configuration between 50 $\Omega$ ports, RF- connected to GND)

| Parameter                                       | Condition                                                                                               | Min  | Тур        | Max        | Unit       |

|-------------------------------------------------|---------------------------------------------------------------------------------------------------------|------|------------|------------|------------|

| Operating Frequency Range                       |                                                                                                         | 100  |            | 3000       | MHz        |

| Minimum Capacitance (C <sub>min</sub> )         | State 00000, 100 MHz (RF+ to Grounded RF-)                                                              | -10% | 1.38       | +10%       | pF         |

| Maximum Capacitance (C <sub>max</sub> )         | State 11111, 100 MHz (RF+ to Grounded RF-)                                                              | -10% | 5.90       | +10%       | pF         |

| Tuning Ratio                                    | C <sub>max</sub> /C <sub>min</sub> , 100 MHz                                                            |      | 4.3:1      |            |            |

| Step Size                                       | 5 bits (32 states), constant step size (100 MHz)                                                        |      | 0.146      |            | pF         |

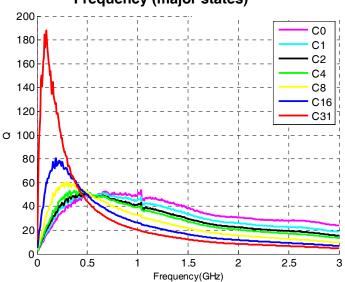

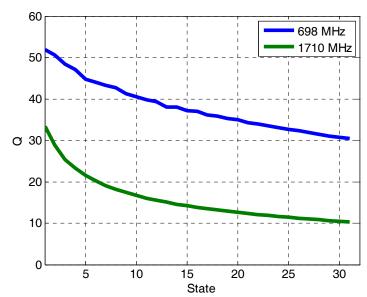

| Quality Factor (C <sub>min</sub> ) <sup>1</sup> | 698 - 960 MHz, with L <sub>s</sub> removed 1710 - 2170 MHz, with L <sub>s</sub> removed                 |      | 50<br>30   |            |            |

| Quality Factor (C <sub>max</sub> ) <sup>1</sup> | 698 - $960$ MHz, with L <sub>s</sub> removed $1710$ - $2170$ MHz, with L <sub>s</sub> removed           |      | 25<br>10   |            |            |

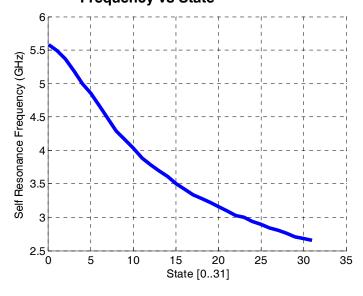

| Self Resonant Frequency                         | State 00000<br>State 11111                                                                              |      | 5.5<br>2.5 |            | GHz        |

| Harmonics <sup>4</sup>                          | 2fo, 3fo: 698 to 915 MHz, Pin +26 dBm, 50 $\Omega$ 2fo, 3fo: 1710 to 1910 MHz, Pin +26 dBm, 50 $\Omega$ |      |            | -36<br>-36 | dBm<br>dBm |

| IMD3                                            | Bands I,II,V/VIII, +20 dBm CW @ TX freq,<br>-15 dBm CW @ 2Tx-Rx freq, 50 Ω                              |      | -111       | -105       | dBm        |

| Switching Time <sup>2,3</sup>                   | State change to 10/90% delta capacitance between any two states                                         |      |            | 10         | μs         |

| Start-up Time <sup>2</sup>                      | Time from V <sub>DD</sub> within specification to all performances within specification                 |      |            | 100        | μs         |

| Wake-up Time <sup>2,3</sup>                     | State change from standby mode to RF state to all performances within specification                     |      |            | 100        | μs         |

Note: 1. Q for a Shunt DTC based on a Series RLC equivalent circuit

$Q = X_C / R = (X-X_L)/R$ , where  $X = X_L + X_C$ ,  $X_L = 2^*pi^*f^*L$ ,  $X_C = -1 / (2^*pi^*f^*C)$ , which is equal to removing the effect of parasitic inductance  $L_S$  2. DC path to ground at RF+ and RF- must be provided to achieve specified performance

<sup>3.</sup> State change activated on falling edge of SEN following data word

<sup>4.</sup> Between 50 Ω ports in series or shunt configuration using a pulsed RF input with 4620 vs period, 50% duty cycle, measured per 3GPPTS45.005

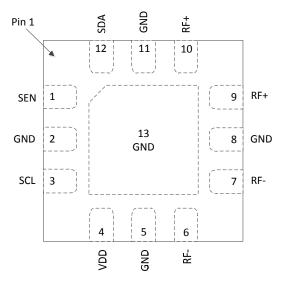

Figure 3. Pin Configuration (Top View)

**Table 2. Pin Descriptions**

| Pin # | Pin Name | Description                        |

|-------|----------|------------------------------------|

| 1     | SEN      | Serial Enable (Active High)        |

| 2     | GND      | Digital and RF Ground              |

| 3     | SCL      | Serial Interface Clock Input       |

| 4     | VDD      | Supply                             |

| 5     | GND      | Digital and RF Ground              |

| 6     | RF-      | Negative RF Port <sup>1</sup>      |

| 7     | RF-      | Negative RF Port <sup>1</sup>      |

| 8     | GND      | Digital and RF Ground <sup>3</sup> |

| 9     | RF+      | Positive RF Port <sup>2</sup>      |

| 10    | RF+      | Positive RF Port <sup>2</sup>      |

| 11    | GND      | Digital and RF Ground              |

| 12    | SDA      | Serial Interface Data Input        |

| 13    | GND      | Digital and RF Ground <sup>3</sup> |

Notes: 1. Pins 6 and 7 must be tied together on PCB board to reduce inductance 2. Pins 9 and 10 must be tied together on PCB board to reduce inductance

3. Pin 2, 5, 8, 11 and 13 must be connected together on PCB

#### **Moisture Sensitivity Level**

The Moisture Sensitivity Level rating for the PE621010 in the 12-lead 2 x 2 QFN package is MSL1.

#### **Latch-Up Avoidance**

Unlike conventional CMOS devices, UltraCMOS® devices are immune to latch-up.

Table 3. Operating Ranges<sup>1</sup>

| Parameter                                                                                                               | Min | Тур | Max         | Unit                                                  |

|-------------------------------------------------------------------------------------------------------------------------|-----|-----|-------------|-------------------------------------------------------|

| V <sub>DD</sub> Supply Voltage                                                                                          | 2.3 | 2.8 | 3.1         | V                                                     |

| I <sub>DD</sub> Power Supply Current <sup>5</sup>                                                                       |     | 30  | 75          | μA                                                    |

| I <sub>DD</sub> Standby Current <sup>5</sup>                                                                            |     | 20  | 45          | μA                                                    |

| Control Voltage High                                                                                                    | 1.2 |     | 3.1         | V                                                     |

| Control Voltage Low                                                                                                     | 0   |     | 0.2         | V                                                     |

| RF Input Power (50Ω) <sup>3,4</sup><br>Shunt                                                                            |     |     | +26         | dBm                                                   |

| Peak Operating RF Voltage <sup>4</sup> V <sub>P</sub> to V <sub>M</sub> V <sub>P</sub> to RFGND V <sub>M</sub> to RFGND |     |     | 6<br>6<br>6 | V <sub>PK</sub><br>V <sub>PK</sub><br>V <sub>PK</sub> |

| Input Control Current                                                                                                   |     | 1   | 10          | μA                                                    |

| Operating Temperature Range                                                                                             | -40 | +25 | +85         | °C                                                    |

| Storage Temperature Range                                                                                               | -65 | +25 | +150        | °C                                                    |

1. Operation should be restricted to the limits in the Operating Ranges table

- 2. The DTC is active when STBY is low (set to 0) and in low-current stand-by mode when high (set to 1)

- 3. Maximum CW power available from a 50Ω source in shunt configuration

- 4. RF+ to RF- and RF+ and/or RF- to ground. Cannot exceed 6 V<sub>PK</sub> or max RF input power (whichever occurs first)

- 5.  $I_{DD}$  current typical value is based on  $V_{DD}$  = 2.8V. Max  $I_{DD}$  is based on  $V_{DD} = 3.1V$

**Table 4. Absolute Maximum Ratings**

| Symbol    | Parameter/Conditions                         | Min | Max  | Unit |

|-----------|----------------------------------------------|-----|------|------|

| $V_{ESD}$ | ESD Voltage (HBM, MIL_STD 883 Method 3015.7) |     | 2000 | ٧    |

Exceeding absolute maximum ratings may cause permanent damage. Operation between operating range maximum and absolute maximum for extended periods may reduce reliability.

#### **Electrostatic Discharge (ESD) Precautions**

When handling this UltraCMOS® device, observe the same precautions that you would use with other ESD-sensitive devices. Although this device contains circuitry to protect it from damage due to ESD, precautions should be taken to avoid exceeding the specified rating.

# Performance Plots @ 25°C and 2.8V unless otherwise specified

Figure 4. Measured Shunt C (@ 100 MHz) vs State (temperature)

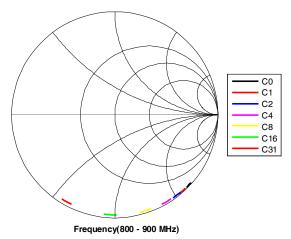

Figure 5. Measured Shunt S<sub>11</sub> (major states)

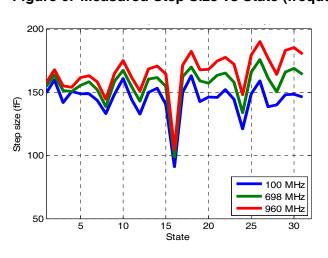

Figure 6. Measured Step Size vs State (frequency)

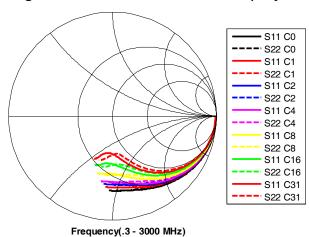

Figure 7. Measured Series  $S_{11}/S_{22}$  (major states)

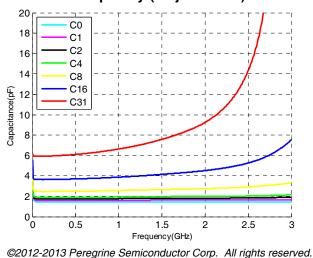

Figure 8. Measured Shunt C vs Frequency (major states)

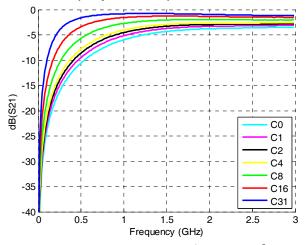

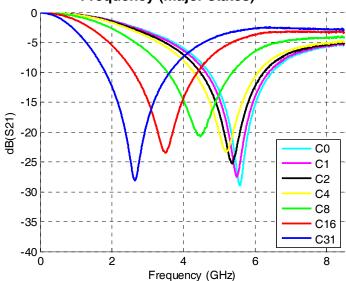

Figure 9. Measured Series S<sub>21</sub> vs Frequency (major states)

Document No. 70-468-02 | UltraCMOS® RFIC Solutions

Figure 10. Measured Shunt Q vs Frequency (major states)

Figure 11. Measured 2-Port Shunt S21 vs Frequency (major states)

Figure 12. Measured Self Resonance Frequency vs State

Figure 13. Measured Shunt Q vs State

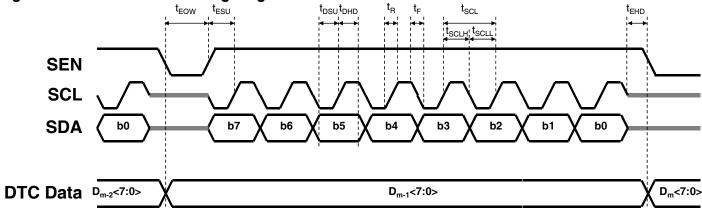

### Serial Interface Operation and Sharing

The PE621010 is controlled by a three wire SPI-compatible interface with enable active high. As shown in *Figure 14*, the serial master initiates the start of a telegram by driving the SEN (Serial Enable) line high. Each bit of the 8-bit telegram (MSB first in) is clocked in on the rising edge of SCL (Serial Clock), as shown in *Table 5* and *Figure 14*. Transitions on SDA (Serial Data) are allowed on the falling edge of SCL. The DTC activates the data on the falling edge of SEN. The DTC does not count how many bits are clocked and only maintains the last 8 bits it received.

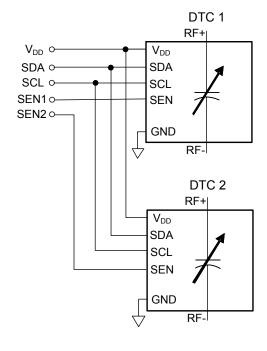

More than 1 DTC can be controlled by one interface by utilizing a dedicated enable (SEN) line for each DTC. SDA, SCL, and V<sub>DD</sub> lines may be shared as shown in *Figure 15*. Dedicated SEN lines act as a chip select such that each DTC will only respond to serial transactions intended for them. This makes each DTC change states sequentially as they are programmed.

Alternatively, a dedicated SDA line with common SEN can be used. This allows all DTCs to change states simultaneously, but requires all DTCs to be programmed even if the state is not changed.

Figure 14. Serial Interface Timing Diagram

Table 5. 8-Bit Serial Programming Register Map

| b7                           | b6             | b5               | b4 | b3 | b2 | b1 | b0      |

|------------------------------|----------------|------------------|----|----|----|----|---------|

| O <sup>1</sup>               | O <sup>1</sup> | STB <sup>2</sup> | d4 | d3 | d2 | d1 | d0      |

| MSB (first in)  LSB (last in |                |                  |    |    |    |    | ast in) |

Note: 1. These bits are reserved and must be written to 0 for proper operation 2. The DTC is active when low (set to 0) and in low-current stand-by mode when high (set to 1)

**Table 6. Serial Interface AC Characteristics**

$2.3V < V_{DD} < 3.1V$ , -40 °C <  $T_A < +85$  °C, unless otherwise specified

| Symbol            | Parameter                            | Min  | Max | Unit |

|-------------------|--------------------------------------|------|-----|------|

| t <sub>SCL</sub>  | Serial Clock Period                  | 38.4 |     | ns   |

| t <sub>SCLL</sub> | SCL Low Time                         | 13.2 |     | ns   |

| t <sub>SCLH</sub> | SCL High Time                        | 13.2 |     | ns   |

| t <sub>R</sub>    | SCL, SDA, SEN Rise Time              |      | 6.5 | ns   |

| t <sub>F</sub>    | SCL, SDA, SEN Fall Time              |      | 6.5 | ns   |

| t <sub>ESU</sub>  | SEN rising edge to SCL rising edge   | 19.2 |     | ns   |

| t <sub>EHD</sub>  | SCL falling edge to SEN falling edge | 19.2 |     | ns   |

| t <sub>DSU</sub>  | SDA valid to SCL rising edge         | 13.2 |     | ns   |

| t <sub>DHD</sub>  | SDA valid after SCL rising edge      | 13.2 |     | ns   |

| t <sub>EOW</sub>  | SEN falling edge to SEN rising edge  | 38.4 |     | ns   |

Figure 15. Recommended Bus sharing

Document No. 70-468-02

UltraCMOS® RFIC Solutions

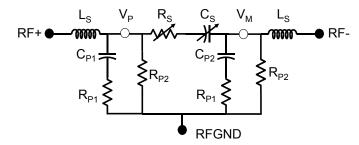

## **Equivalent Circuit Model Description**

The DTC Equivalent Circuit Model includes all parasitic elements and is accurate in both Series and Shunt configurations, reflecting physical circuit behavior accurately and providing very close correlation to measured data. It can easily be used in circuit simulation programs. Simple equations are provided for the state dependent parameters.

The Tuning Core capacitance C<sub>S</sub> represents capacitance between RF+ and RF- ports. It is linearly proportional to state (0 to 31 in decimal) in a discrete fashion. The Series Tuning Ratio is defined as C<sub>Smax</sub>/C<sub>Smin</sub>.

C<sub>P1</sub> and C<sub>P2</sub> represent the circuit and package parasitics from RF ports to GND. In shunt configuration the total capacitance of the DTC is higher due to parallel combination of  $C_P$  and  $C_S$ . The capacitance seen looking into RF+ is C<sub>S</sub>+C<sub>P1</sub> (when RF- is grounded) and C<sub>S</sub>+C<sub>P2</sub> for RF-, respectively. In Series configuration, C<sub>S</sub> and C<sub>P</sub> do not add in parallel and the DTC appears as an impedance transformation network.

Parasitic inductance due to circuit and package is modeled as L<sub>S</sub> and causes the apparent capacitance of the DTC to increase with frequency until it reaches Self Resonant Frequency (SRF). The value of SRF depends on state and is approximately inversely proportional to the square root of capacitance.

The overall dissipative losses of the DTC are modeled by R<sub>S</sub>, R<sub>P1</sub> and R<sub>P2</sub> resistors. The parameter R<sub>S</sub> represents the Equivalent Series Resistance (ESR) of the tuning core and is dependent on state. R<sub>P1</sub> and R<sub>P2</sub> represent losses due to the parasitic and biasing networks.

**Table 7. Maximum Operating RF Voltage**

| Condition               | Limit             |

|-------------------------|-------------------|

| $V_P$ to $V_M$          | 6 V <sub>PK</sub> |

| V <sub>P</sub> to RFGND | 6 V <sub>PK</sub> |

| V <sub>M</sub> to RFGND | 6 V <sub>PK</sub> |

Figure 16. Equivalent Circuit Model Schematic

**Table 8. Equivalent Circuit Model Parameters**

| Variable        | <b>Equation</b> (state = 0, 1, 231) | Unit |

|-----------------|-------------------------------------|------|

| Cs              | 0.148*state + 0.97                  | pF   |

| Rs              | 30/(state+30/(state+0.4)) + 0.4     | Ω    |

| R <sub>P1</sub> | 4                                   | Ω    |

| $R_{P2}$        | 22000 + 6*(state)^3                 | Ω    |

| C <sub>P1</sub> | -0.0022*state + 0.400               | pF   |

| $C_{P2}$        | 0.0026*state + 0.509                | pF   |

| Ls              | 0.4                                 | nH   |

Table 9. Equivalent Circuit Data

| State                                                        |       | DTC | Core       | Paras     | sitic Elen  | nents       |             |

|--------------------------------------------------------------|-------|-----|------------|-----------|-------------|-------------|-------------|

| Hex                                                          | Bin   | Dec | Cs<br>[pF] | Rs<br>[Ω] | Cp1<br>[pF] | Cp2<br>[pF] | Rp2<br>[kΩ] |

| 0x00                                                         | 00000 | 0   | 0.97       | 0.80      | 0.40        | 0.51        | 22.0        |

| 0x01                                                         | 00001 | 1   | 1.12       | 1.73      | 0.40        | 0.51        | 22.0        |

| 0x02                                                         | 00010 | 2   | 1.27       | 2.41      | 0.40        | 0.51        | 22.0        |

| 0x03                                                         | 00011 | 3   | 1.41       | 2.81      | 0.39        | 0.52        | 22.2        |

| 0x04                                                         | 00100 | 4   | 1.56       | 2.98      | 0.39        | 0.52        | 22.4        |

| 0x05                                                         | 00101 | 5   | 1.71       | 3.00      | 0.39        | 0.52        | 22.8        |

| 0x06                                                         | 00110 | 6   | 1.86       | 2.92      | 0.39        | 0.52        | 23.3        |

| 0x07                                                         | 00111 | 7   | 2.01       | 2.81      | 0.39        | 0.53        | 24.1        |

| 0x08                                                         | 01000 | 8   | 2.15       | 2.68      | 0.38        | 0.53        | 25.1        |

| 0x09                                                         | 01001 | 9   | 2.30       | 2.54      | 0.38        | 0.53        | 26.4        |

| 0x0A                                                         | 01010 | 10  | 2.45       | 2.42      | 0.38        | 0.54        | 28.0        |

| 0x0B                                                         | 01011 | 11  | 2.60       | 2.29      | 0.38        | 0.54        | 30.0        |

| 0x0C                                                         | 01100 | 12  | 2.75       | 2.18      | 0.37        | 0.54        | 32.4        |

| 0x0D                                                         | 01101 | 13  | 2.89       | 2.08      | 0.37        | 0.54        | 35.2        |

| 0x0E                                                         | 01110 | 14  | 3.04       | 1.99      | 0.37        | 0.55        | 38.5        |

| 0x0F                                                         | 01111 | 15  | 3.19       | 1.90      | 0.37        | 0.55        | 42.3        |

| 0x10                                                         | 10000 | 16  | 3.34       | 1.83      | 0.37        | 0.55        | 46.6        |

| 0x11                                                         | 10001 | 17  | 3.49       | 1.76      | 0.36        | 0.55        | 51.5        |

| 0x12                                                         | 10010 | 18  | 3.63       | 1.69      | 0.36        | 0.56        | 57.0        |

| 0x13                                                         | 10011 | 19  | 3.78       | 1.63      | 0.36        | 0.56        | 63.2        |

| 0x14                                                         | 10100 | 20  | 3.93       | 1.58      | 0.36        | 0.56        | 70.0        |

| 0x15                                                         | 10101 | 21  | 4.08       | 1.53      | 0.35        | 0.56        | 77.6        |

| 0x16                                                         | 10110 | 22  | 4.23       | 1.48      | 0.35        | 0.57        | 85.9        |

| 0x17                                                         | 10111 | 23  | 4.37       | 1.44      | 0.35        | 0.57        | 95.0        |

| 0x18                                                         | 11000 | 24  | 4.52       | 1.40      | 0.35        | 0.57        | 104.9       |

| 0x19                                                         | 11001 | 25  | 4.67       | 1.36      | 0.35        | 0.57        | 115.8       |

| 0x1A                                                         | 11010 | 26  | 4.82       | 1.33      | 0.34        | 0.58        | 127.4       |

| 0x1B                                                         | 11011 | 27  | 4.97       | 1.30      | 0.34        | 0.58        | 140.1       |

| 0x1C                                                         | 11100 | 28  | 5.11       | 1.27      | 0.34        | 0.58        | 153.7       |

| 0x1D                                                         | 11101 | 29  | 5.26       | 1.24      | 0.34        | 0.58        | 168.3       |

| 0x1E                                                         | 11110 | 30  | 5.41       | 1.21      | 0.33        | 0.59        | 184.0       |

| 0x1F                                                         | 11111 | 31  | 5.56       | 1.19      | 0.33        | 0.59        | 200.7       |

| @2010 2012 Paragrina Camigandustar Carn. All rights recogned |       |     |            |           |             |             |             |

©2012-2013 Peregrine Semiconductor Corp. All rights reserved.

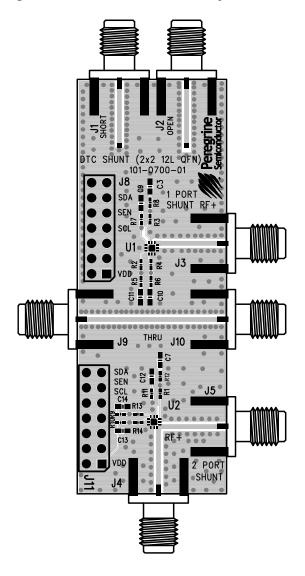

#### **Evaluation Board**

The 101-0700 Evaluation Board (EVB) was designed for accurate measurement of the DTC impedance and loss. Two configurations are available: 1 Port Shunt (J3) and 2 Port Shunt (J4, J5). Three calibration standards are provided. The open (J2) and short (J1) standards (104 ps delay) are used for performing port extensions and accounting for electrical length and transmission line loss. The Thru (J9, J10) standard can be used to estimate PCB transmission line losses for scalar de-embedding of the 2 Port Shunt configuration (J4, J5).

The board consists of a 4 layer stack with 2 outer layers made of Rogers 4350B ( $\epsilon_r$  = 3.48) and 2 inner layers of FR4 ( $\epsilon_r$  = 4.80). The total thickness of this board is 62 mils (1.57 mm). The inner layers provide a ground plane for the transmission lines. Each transmission line is designed using a coplanar waveguide with ground plane (CPWG) model using a trace width of 32 mils (0.813 mm), gap of 15 mils (0.381 mm), and a metal thickness of 1.4 mils (0.036 mm).

Figure 17. Evaluation Board Layout

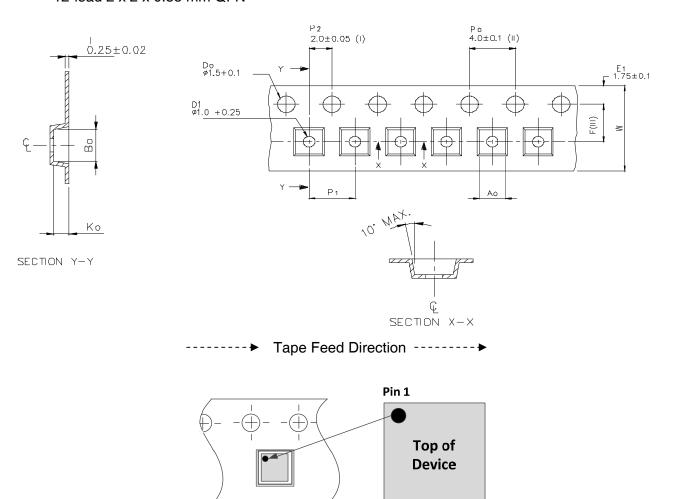

Figure 18. Package Drawing

12-lead 2 x 2 x 0.55 mm QFN

N

NOTES

A. DIMENSIONS ARE IN MILLIMETERS

B. DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 1994

Figure 19. Top Marking Specifications

| Marking Spec<br>Symbol | Package<br>Marking | Definition                                                           |  |  |

|------------------------|--------------------|----------------------------------------------------------------------|--|--|

| PP                     | CN                 | Part number marking for PE621010                                     |  |  |

| ZZ                     | 00-99              | Last two digits of lot code                                          |  |  |

| Y                      | 0-9                | Last digit of year, starting from 2009 (0 for 2010, 1 for 2011, etc) |  |  |

| ww                     | 01-53              | Work week                                                            |  |  |

17-0112

Figure 20. Tape and Reel Specifications 12-lead 2 x 2 x 0.55 mm QFN

**Device Orientation in Tape**

**Table 10. Ordering Information**

| Order Code     | Package                     | Description                   | Shipping Method   |

|----------------|-----------------------------|-------------------------------|-------------------|

| PE621010MLAA-Z | 12-lead 2 x 2 x 0.55 mm QFN | Package Part in Tape and Reel | 3,000 units / T&R |

| EK621010-11    | Evaluation Kit              | Evaluation Kit                | 1 set / box       |

#### **Sales and Contact Information**

For sales and contact information please visit www.psemi.com.

Advance Information: The product is in a formative or design stage. The datasheet contains design target specifications for product development. Specifications and features may change in any manner without notice. Preliminary Specification: The datasheet contains preliminary data. Additional data may be added at a later date. Peregrine reserves the right to change specifications at any time without notice in order to supply the best possible product. Product Specification: The datasheet contains final data. In the event Peregrine decides to change the specifications, Peregrine will notify customers of the intended changes by issuing a CNF (Customer Notification Form).

The information in this datasheet is believed to be reliable. However, Peregrine assumes no liability for the use of this information. Use shall be entirely at the user's own risk.

No patent rights or licenses to any circuits described in this datasheet are implied or granted to any third party. Peregrine's products are not designed or intended for use in devices or systems intended for surgical implant, or in other applications intended to support or sustain life, or in any application in which the failure of the Peregrine product could create a situation in which personal injury or death might occur. Peregrine assumes no liability for damages, including consequential or incidental damages, arising out of the use of its products in such applications.

such applications.

The Peregrine name, logo, UltraCMOS and UTSi are registered trademarks and HaRP, MultiSwitch and DuNE are trademarks of Peregrine Semiconductor Corp.

Document No. 70-468-02 | UltraCMOS® RFIC Solutions